Non, cela provoque simplement un blocage du processeur.

Que se passe-t-il si le cache est manquant ?

Lorsqu’un manque de cache se produit, le système ou l’application procède à la localisation des données dans le magasin de données sous-jacent, ce qui augmente la durée de la demande. En règle générale, le système peut écrire les données dans le cache, augmentant à nouveau la latence, bien que cette latence soit compensée par les accès au cache sur d’autres données.

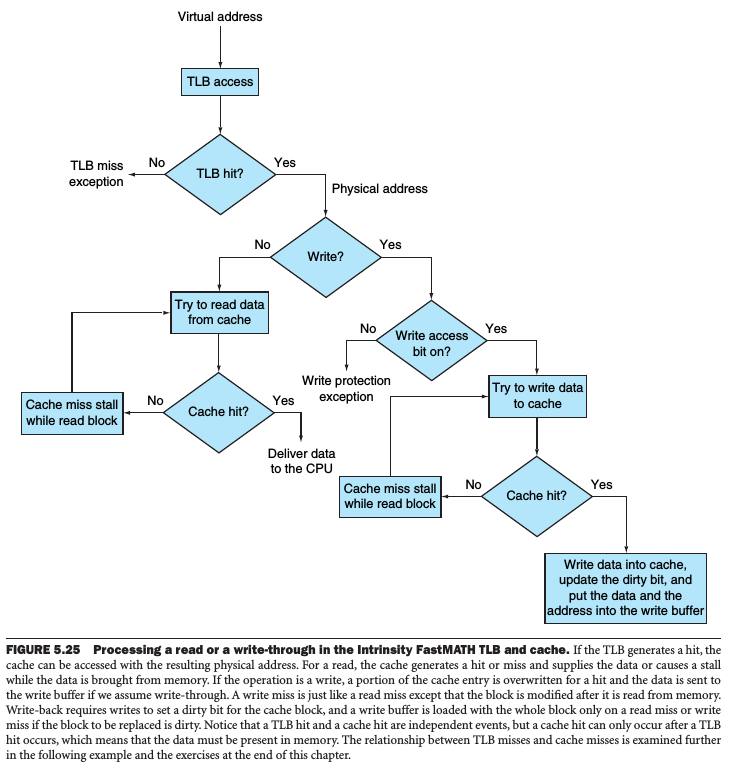

L’absence de cache est-elle identique à l’erreur de page ?

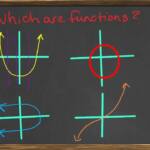

Un programme recherche une page dans le TLB, s’il ne trouve pas cette page, c’est un échec du TLB, puis il recherche la page dans le cache. Si la page n’est pas dans le cache, il s’agit d’un manque de cache et recherche ensuite la page dans la RAM. Si la page n’est pas dans la RAM, il s’agit d’un défaut de page et le programme recherche les données dans le stockage secondaire.

Est-ce qu’un TLB manque un défaut de page ?

Cache Miss, TLB Miss et Page Fault Si cela correspond, il s’agit d’un accès au cache. Sinon, c’est un manque de cache. Dans ce cas, nous utilisons l’adresse physique pour obtenir le bloc de la mémoire et le cache sera mis à jour. L’échec du TLB se produit si nous ne trouvons pas la page dans le TLB.

Que se passe-t-il si le cache manque ?

Lorsqu’un manque de cache se produit, le système ou l’application procède à la localisation des données dans le magasin de données sous-jacent, ce qui augmente la durée de la demande. En règle générale, le système peut écrire les données dans le cache, augmentant à nouveau la latence, bien que cette latence soit compensée par les accès au cache sur d’autres données.

Est-ce qu’un TLB manque un défaut de page ?

Cache Miss, TLB Miss et Page Fault Si cela correspond, il s’agit d’un accès au cache. Sinon, c’est un manque de cache. Dans ce cas, nous utilisons l’adresse physique pour obtenir le bloc de la mémoire et le cache sera mis à jour. L’échec du TLB se produit si nous ne trouvons pas la page dans le TLB.

Quelle est la différence entre un succès de cache et un échec de cache ?

Qu’est-ce que Cache Miss and Hit ?Un échec de cache se produit lorsqu’un cache n’a pas les données demandées dans sa mémoire. Pendant ce temps, un hit se produit lorsqu’un cache trouve avec succès les données demandées, satisfaisant la requête de recherche. Pour un système de mise en cache plus efficace, le taux de succès doit être supérieur au taux d’échecs.

Comment l’absence de cache est-elle calculée ?

La meilleure façon de calculer un taux d’accès au cache consiste à diviser le nombre total d’accès au cache par la somme du nombre total d’accès au cache et du nombre d’échecs au cache.

Quels sont les 3 C dans le cache manqué ?

Les trois C des caches Manque obligatoire : l’objet n’a jamais été dans la cache. Manque de capacité : l’élément était dans le cache, mais l’espace était restreint et il a été expulsé. Conflit manqué : l’élément était dans le cache, mais le cache n’était pas assez associatif, il a donc été forcé.

Qu’est-ce qu’un raté de cache obligatoire ?

Un échec obligatoire fait référence à l’échec du cache qui se produit lorsque le premier accès à un bloc n’est pas dans le cache, donc le bloc doit être mis dans le cache.

Le taux d’échec du cache est-il un bon indicateur de performances ?

Selon cet article, les erreurs de cache aux instructions sont un bon indicateur des performances du cache. Le rapport entre les échecs de cache et les instructions donnera une indication du bon fonctionnement du cache ; plus le rapport est bas, mieux c’est.

Qu’est-ce que la raclée signifie ?

Le thrashing est une activité informatique qui progresse peu ou pas, généralement parce que la mémoire ou d’autres ressources sont épuisées ou trop limitées pour effectuer les opérations nécessaires.

Que se passe-t-il après l’accès au cache ?

Un accès au cache décrit la situation dans laquelle le contenu de votre site est servi avec succès à partir du cache. Les balises sont rapidement recherchées dans la mémoire, et lorsque les données sont trouvées et lues, elles sont considérées comme un accès au cache. Un accès au cache se produit lorsque le contenu est servi avec succès à partir dele cache au lieu du serveur.

L’absence de cache a-t-elle un effet sur les performances du pipeline ?

Effets de latence de la mémoire : dans un processeur monothread, le pipeline d’exécution doit se bloquer lorsqu’un défaut de cache externe se produit. L’effet est de retarder l’instruction incriminée et toute autre instruction actuellement dans le pipeline.

Qu’est-ce qu’un manque de cache CPU ?

Un échec de cache est une tentative infructueuse de lire ou d’écrire une donnée dans le cache, ce qui entraîne un accès à la mémoire principale avec une latence beaucoup plus longue. Il existe trois types d’échecs de cache : échec de lecture d’instruction, échec de lecture de données et échec d’écriture de données.

Que se passe-t-il si le cache manque ?

Lorsqu’un manque de cache se produit, le système ou l’application procède à la localisation des données dans le magasin de données sous-jacent, ce qui augmente la durée de la demande. En règle générale, le système peut écrire les données dans le cache, augmentant à nouveau la latence, bien que cette latence soit compensée par les accès au cache sur d’autres données.

Est-ce qu’un TLB manque un défaut de page ?

Cache Miss, TLB Miss et Page Fault Si cela correspond, il s’agit d’un accès au cache. Sinon, c’est un manque de cache. Dans ce cas, nous utilisons l’adresse physique pour obtenir le bloc de la mémoire et le cache sera mis à jour. L’échec du TLB se produit si nous ne trouvons pas la page dans le TLB.

Qu’est-ce qu’un moyen de réduire la pénalité d’échec ?

Le cache de premier niveau plus petit pour tenir sur la puce avec le CPU et assez rapide pour traiter les requêtes en un ou deux cycles d’horloge du CPU. Hits pour de nombreux accès à la mémoire qui iraient à la mémoire principale, réduisant la pénalité effective en cas d’échec.

Qu’est-ce qu’un manque de conflit ?

Conflit manqué : lorsqu’il y a encore des lignes vides dans le cache, le bloc de mémoire principale est en conflit avec la ligne déjà remplie du cache, c’est-à-dire que même lorsqu’un espace vide est disponible, le bloc essaie d’occuper une ligne déjà remplie.c’est ce qu’on appelle le conflit manqué. Manque de capacité : un manque s’est produit lorsque toutes les lignes du cache sont remplies.

Combien y a-t-il d’entrées dans TLB ?

Un TLB est organisé comme un cache entièrement associatif et contient généralement de 16 à 512 entrées. Chaque entrée TLB contient un numéro de page virtuelle et son numéro de page physique correspondant. Le TLB est accessible à l’aide du numéro de page virtuelle. Si le TLB arrive, il renvoie le numéro de page physique correspondant.

Quel est le but du TLB ?

Un tampon de recherche de traduction (TLB) est un cache mémoire qui stocke les traductions récentes de la mémoire virtuelle vers des adresses physiques pour une récupération plus rapide. Lorsqu’une adresse de mémoire virtuelle est référencée par un programme, la recherche démarre dans le CPU. Tout d’abord, les caches d’instructions sont vérifiés.

Quelle est la différence entre l’espace utilisateur et l’espace noyau ?

L’espace du noyau est strictement réservé à l’exécution d’un noyau de système d’exploitation privilégié, d’extensions de noyau et de la plupart des pilotes de périphériques. En revanche, l’espace utilisateur est la zone de mémoire où s’exécutent les logiciels d’application et certains pilotes.

Qu’est-ce qu’un manque de cache ?

Une erreur de cache oblige le système ou l’application à effectuer une seconde tentative pour localiser les données, cette fois par rapport à la base de données principale plus lente. Si les données sont trouvées dans la base de données principale, les données sont alors généralement copiées dans le cache en prévision d’une autre demande à venir pour ces mêmes données.

Que se passe-t-il en cas d’absence de cache sur un VLIW ?

(Une exception inhabituelle serait un pipeline basé sur push tel qu’utilisé par certains premiers VLIW. Ces opérations ultérieures nécessaires pour pousser les opérations précédentes dans les pipelines.) Pour un échec de cache sur un magasin, la valeur stockée peut être placée dans un tampon permettant au magasin de se terminer malgré l’échec du cache.

Qu’est-ce qu’un taux d’échec et d’accès au cache ?

Un manque de cache se produit lorsqu’uncache n’a pas les données demandées dans sa mémoire. Pendant ce temps, un hit se produit lorsqu’un cache trouve avec succès les données demandées, satisfaisant la requête de recherche. Pour un système de mise en cache plus efficace, le taux de réussite doit être supérieur au taux d’échec. L’un des meilleurs moyens d’y parvenir est de réduire les échecs de cache.

Les échecs de cache augmentent-ils la latence ?

Les échecs de cache ajouteront une latence qui, autrement, n’aurait pas été encourue dans un système sans cache. Cependant, dans un cache correctement configuré, les avantages de vitesse obtenus grâce aux accès au cache compensent largement le temps perdu sur les échecs du cache.