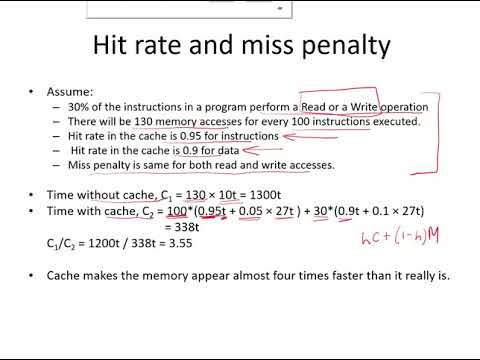

Miss Penalty fait référence au temps supplémentaire nécessaire pour mettre les données en cache à partir de la mémoire principale chaque fois qu’il y a un « manquement » dans le cache. Miss Penalty est le temps nécessaire pour récupérer les données une fois que vous manquez dans le cache. Étant donné que nous avons affaire à un cache à un seul niveau, le seul autre niveau de la hiérarchie de la mémoire à prendre en compte est la mémoire principale pour la pénalité d’échec.

Qu’entend-on par pénalité d’échec de cache ?

La pénalité d’échec est définie comme la différence entre le temps d’accès au niveau inférieur et le temps d’accès au cache. Ensuite, l’équation ci-dessus devient effective-access-time = cache-access-time + miss-rate * miss-penalty.

Comment la pénalité d’échec est-elle calculée dans le cache ?

Vous pouvez calculer la pénalité d’échec de la manière suivante en utilisant une moyenne pondérée : (0,5 * 0ns) + (0,5 * 500ns) = (0,5 * 500ns) = 250ns . Maintenant, supposons que vous ayez un cache à plusieurs niveaux, c’est-à-dire un cache L1 et L2. Le temps de réponse représente désormais le temps nécessaire pour récupérer les données dans le cache L1.

Qu’est-ce qu’un défaut de mise en cache ?

Un échec de cache est un événement dans lequel un système ou une application demande de récupérer des données à partir d’un cache, mais ces données spécifiques ne sont pas actuellement dans la mémoire cache. Comparez cela à un accès au cache, dans lequel les données demandées sont extraites avec succès du cache.

Quel est le taux d’échec dans la mémoire cache ?

De même, le taux d’échec est le nombre total d’échecs de cache divisé par le nombre total de requêtes de mémoire adressées au cache. On peut également calculer le nombre de succès ou d’échecs sur les lectures ou les écritures uniquement. De toute évidence, un taux de réussite plus élevé se traduira généralement par de meilleures performances.

Qu’entend-on par pénalité d’échec de cache ?

La pénalité d’échec est définie comme la différence entre le temps d’accès au niveau inférieur et le temps d’accès au cache. Alors l’équation ci-dessus devient effective-access-time = cache-temps d’accès + taux d’échec * pénalité d’échec.

Comment la pénalité d’échec est-elle calculée dans le cache ?

Vous pouvez calculer la pénalité d’échec de la manière suivante en utilisant une moyenne pondérée : (0,5 * 0ns) + (0,5 * 500ns) = (0,5 * 500ns) = 250ns . Maintenant, supposons que vous ayez un cache à plusieurs niveaux, c’est-à-dire un cache L1 et L2. Le temps d’accès représente désormais le temps nécessaire pour récupérer les données dans le cache L1.

Quelle est la pénalité d’échec de la mémoire principale en cycles ?

La pénalité d’échec est le temps nécessaire pour copier les données de la mémoire principale vers le cache. Cela nécessite souvent des dizaines de cycles d’horloge (au moins). Le taux de ratés est le pourcentage de ratés. Le temps moyen d’accès à la mémoire, ou AMAT, peut alors être calculé.

Que sont les caches L1 L2 et L3 ?

La principale différence entre le cache L1 L2 et L3 est que le cache L1 est la mémoire cache la plus rapide et le cache L3 est la mémoire cache la plus lente tandis que le cache L2 est plus lent que le cache L1 mais plus rapide que le cache L3. Le cache est une mémoire rapide dans l’ordinateur. Il contient les données fréquemment utilisées par le CPU.

Qu’est-ce qu’un bon taux d’accès au cache ?

Un taux d’accès au cache de 90 % et plus signifie que la plupart des requêtes sont satisfaites par le cache. Une valeur inférieure à 80 % sur les fichiers statiques indique une mise en cache inefficace en raison d’une mauvaise configuration.

Comment réduisez-vous la capacité des ratés ?

Les échecs de cache peuvent être réduits en modifiant la capacité, la taille des blocs et/ou l’associativité. La première étape pour réduire le taux d’échec consiste à comprendre les causes des échecs. Les échecs peuvent être classés comme obligatoires, de capacité et de conflit.

L’absence de cache est-elle une exception ?

Non, cela provoque simplement un blocage du processeur. Peut-être qu’une image mentale appropriée est celle d’une ou plusieurs instructions NOP insérées dans le pipeline.

Comment le taux d’échec et la pénalité d’échec sont-ils minimisés ?

Le plus petit cache de premier niveau pour s’adapter à la puceavec le CPU et suffisamment rapide pour traiter les requêtes en un ou deux cycles d’horloge du CPU. Hits pour de nombreux accès à la mémoire qui iraient à la mémoire principale, réduisant la pénalité effective en cas d’échec.

Quelle est la lenteur d’un échec de cache ?

Un échec de cache se produit lorsqu’un cache n’a pas les données demandées dans sa mémoire. Pendant ce temps, un hit se produit lorsqu’un cache trouve avec succès les données demandées, satisfaisant la requête de recherche. Pour un système de mise en cache plus efficace, le taux de succès doit être supérieur au taux d’échecs.

Comment réduire le taux d’échec du cache ?

Les échecs de cache peuvent être réduits en modifiant la capacité, la taille des blocs et/ou l’associativité. La première étape pour réduire le taux d’échec consiste à comprendre les causes des échecs. Les échecs peuvent être classés comme obligatoires, de capacité et de conflit.

Combien de cycles un échec de cache prend-il ?

Un échec L2 correspond à au moins 600 cycles. Le cache est tout en performance ; Les processeurs sont tellement plus rapides que la mémoire maintenant que vous optimisez presque pour le bus mémoire au lieu du cœur.

Quelle technique est utilisée pour réduire la pénalité d’échec pour améliorer les performances du cache ?

Jetons un coup d’œil à d’autres techniques pour réduire la pénalité d’échec. Cette technique est utilisée avec écriture immédiate ou écriture différée. L’idée n’est pas de faire attendre le CPU que l’écriture se termine en mémoire. Au lieu de cela, les données sont écrites dans un tampon d’écriture et le processeur peut continuer pendant qu’elles sont écrites dans la mémoire.

Comment éviter les ratés obligatoires ?

Une façon de réduire le nombre de capacités et d’échecs obligatoires consiste à utiliser des techniques de prélecture telles que des tailles de ligne de cache plus longues ou des méthodes de prélecture [9, 1]. Cependant, les tailles de ligne ne peuvent pas être rendues arbitrairement grandes sans augmenter le taux d’échec et augmenter considérablement la quantité de données à transférer.06.08.1990

Qu’entend-on par pénalité d’échec de cache ?

La pénalité d’échec est définie comme la différence entre le temps d’accès au niveau inférieur et le temps d’accès au cache. Ensuite, l’équation ci-dessus devient effective-access-time = cache-access-time + miss-rate * miss-penalty.

Comment la pénalité d’échec est-elle calculée dans le cache ?

Vous pouvez calculer la pénalité d’échec de la manière suivante en utilisant une moyenne pondérée : (0,5 * 0ns) + (0,5 * 500ns) = (0,5 * 500ns) = 250ns . Maintenant, supposons que vous ayez un cache à plusieurs niveaux, c’est-à-dire un cache L1 et L2. Le temps d’accès représente désormais le temps nécessaire pour récupérer les données dans le cache L1.

Qu’est-ce qu’un défaut de mise en cache ?

Un échec de cache est un événement dans lequel un système ou une application demande de récupérer des données à partir d’un cache, mais ces données spécifiques ne sont pas actuellement dans la mémoire cache. Comparez cela à un accès au cache, dans lequel les données demandées sont extraites avec succès du cache.

Quelle est la pénalité d’échec, c’est-à-dire le temps nécessaire pour remplir un bloc de cache en termes de cycles d’horloge du processeur ?

Qu’est-ce qu’un manque de cache ?

Une erreur de cache oblige le système ou l’application à effectuer une seconde tentative pour localiser les données, cette fois par rapport à la base de données principale plus lente. Si les données sont trouvées dans la base de données principale, les données sont alors généralement copiées dans le cache en prévision d’une autre demande à venir pour ces mêmes données.

Quelles sont les composantes d’une pénalité pour raté ?

Cela inclut le temps nécessaire pour accéder au bloc, le transmettre d’un niveau à l’autre, l’insérer dans le niveau qui a subi l’échec, puis transmettre le bloc au demandeur. Le temps nécessaire pour accéder au niveau suivant dans la hiérarchie est l’élément majeur de la pénalité pour échec.

Comment calculez-vous le taux d’échec d’un cache à un seul niveau ?

Parce que nous avons affaire à un cache à un seul niveau, le seul autre niveau dans lela hiérarchie de mémoire à considérer est la mémoire principale pour la pénalité de raté. Voici un bon exemple de cache à un niveau : le cache L1 a un temps d’accès de 5 ns et un taux d’échec de 50 % La mémoire principale a un temps d’accès de 500 ns AMAT = 5 ns + 0,5 * 500 ns = 255 ns

Les échecs de cache augmentent-ils la latence ?

Les échecs de cache ajouteront une latence qui, autrement, n’aurait pas été encourue dans un système sans cache. Cependant, dans un cache correctement configuré, les avantages de vitesse obtenus grâce aux accès au cache compensent largement le temps perdu sur les échecs du cache.