No, it simply causes a processor stall.

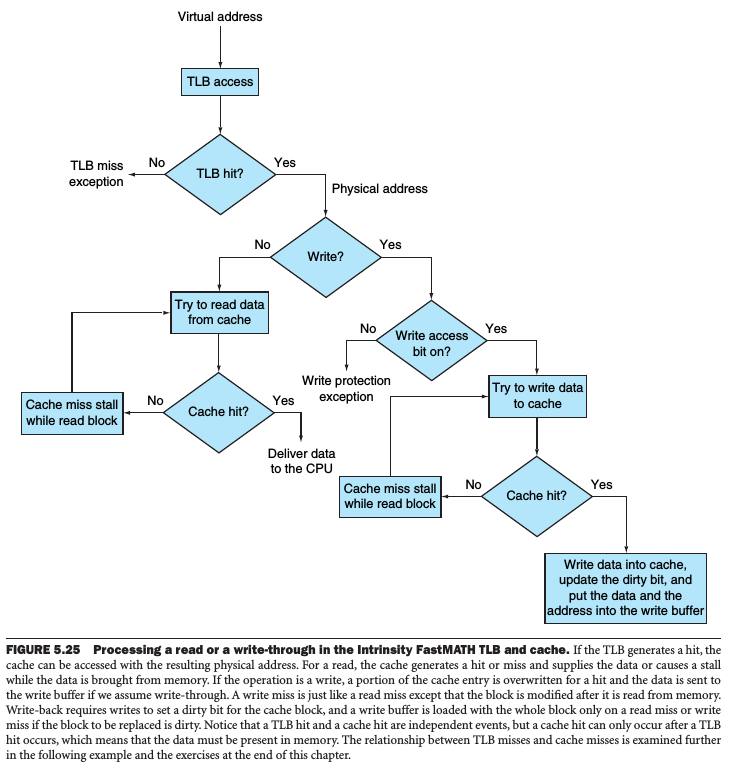

What happens if cache miss?

When a cache miss occurs, the system or application proceeds to locate the data in the underlying data store, which increases the duration of the request. Typically, the system may write the data to the cache, again increasing the latency, though that latency is offset by the cache hits on other data.

Is cache miss same as page fault?

A program search for a page in TLB, if it doesn’t find that page it’s a TLB miss and then further looks for the page in cache. If the page is not in cache then it’s a cache miss and further looks for the page in RAM. If the page is not in RAM, then it’s a page fault and program look for the data in secondary storage.

Is a TLB miss a page fault?

Cache Miss, TLB Miss, and Page Fault If it matches, it’s a cache hit. Otherwise, it’s a cache miss. In this case, we use the physical address to get the block from memory, and the cache will be updated. TLB miss occurs if we don’t find the page inside the TLB.

What happens if cache miss?

When a cache miss occurs, the system or application proceeds to locate the data in the underlying data store, which increases the duration of the request. Typically, the system may write the data to the cache, again increasing the latency, though that latency is offset by the cache hits on other data.

Is a TLB miss a page fault?

Cache Miss, TLB Miss, and Page Fault If it matches, it’s a cache hit. Otherwise, it’s a cache miss. In this case, we use the physical address to get the block from memory, and the cache will be updated. TLB miss occurs if we don’t find the page inside the TLB.

What is the difference between cache hit and cache miss?

What Is Cache Miss and Hit? A cache miss occurs when a cache doesn’t have the requested data in its memory. Meanwhile, a hit is when a cache successfully finds the requested data, satisfying the search query. For a more effective caching system, the hit ratio should be higher than the miss rate.

How is cache miss calculated?

The best way to calculate a cache hit ratio is to divide the total number of cache hits by the sum of the total number of cache hits, and the number of cache misses.

What is the 3 Cs in cache miss?

The Three C s of Caches Compulsory miss: item has never been in the cache. Capacity miss: item has been in the cache, but space was tight and it was forced out. Conflict miss: item was in the cache, but the cache was not associative enough, so it was forced out.

What is a compulsory cache miss?

A compulsory miss refers to the cache miss that happens when the first access to a block is not in the cache, so the block must be brought into the cache.

Is cache miss rate a good indicator of performance?

According to this article the cache-misses to instructions is a good indicator of cache performance. The ratio of cache-misses to instructions will give an indication how well the cache is working; the lower the ratio the better.

What thrashing means?

Thrashing is computer activity that makes little or no progress, usually because memory or other resources have become exhausted or too limited to perform needed operations.

What happens after cache hit?

A cache hit describes the situation where your site’s content is successfully served from the cache. The tags are searched in the memory rapidly, and when the data is found and read, it’s considered as a cache hit. A cache hit is when content is successfully served from the cache instead of the server.

Is there any effect of cache miss on pipeline performance?

Memory Latency Effects: In a single-threaded processor, the execution pipeline must stall when an external cache miss occurs. The effect is to delay the offending instruction and any other instructions currently in the pipeline.

What is a CPU cache miss?

A cache miss is a failed attempt to read or write a piece of data in the cache, which results in a main memory access with much longer latency. There are three kinds of cache misses: instruction read miss, data read miss, and data write miss.

What happens if cache miss?

When a cache miss occurs, the system or application proceeds to locate the data in the underlying data store, which increases the duration of the request. Typically, the system may write the data to the cache, again increasing the latency, though that latency is offset by the cache hits on other data.

Is a TLB miss a page fault?

Cache Miss, TLB Miss, and Page Fault If it matches, it’s a cache hit. Otherwise, it’s a cache miss. In this case, we use the physical address to get the block from memory, and the cache will be updated. TLB miss occurs if we don’t find the page inside the TLB.

What is a way to reduce the miss penalty?

The smaller first-level cache to fit on the chip with the CPU and fast enough to service requests in one or two CPU clock cycles. Hits for many memory accesses that would go to main memory, lessening the effective miss penalty.

What is conflict miss?

Conflict miss: when still there are empty lines in the cache, block of main memory is conflicting with the already filled line of cache, ie., even when empty place is available, block is trying to occupy already filled line. its called conflict miss. Capacity miss: miss occured when all lines of cache are filled.

How many entries are in TLB?

A TLB is organized as a fully associative cache and typically holds 16 to 512 entries. Each TLB entry holds a virtual page number and its corresponding physical page number. The TLB is accessed using the virtual page number. If the TLB hits, it returns the corresponding physical page number.

What is the purpose of TLB?

A translation lookaside buffer (TLB) is a memory cache that stores recent translations of virtual memory to physical addresses for faster retrieval. When a virtual memory address is referenced by a program, the search starts in the CPU. First, instruction caches are checked.

What is the difference between user space and kernel space?

Kernel space is strictly reserved for running a privileged operating system kernel, kernel extensions, and most device drivers. In contrast, user space is the memory area where application software and some drivers execute.

What is a cache miss?

A cache miss requires the system or application to make a second attempt to locate the data, this time against the slower main database. If the data is found in the main database, the data is then typically copied into the cache in anticipation of another near-future request for that same data.

What happens if there is a cache miss on a VLIW?

(An unusual exception would be a push-based pipeline as used by some early VLIWs. Such required subsequent operations to push previous operations down the pipelines.) For a cache miss on a store, the stored value can be placed into a buffer allowing the store to complete despite the cache miss.

What is a cache miss and hit ratio?

A cache miss occurs when a cache doesn’t have the requested data in its memory. Meanwhile, a hit is when a cache successfully finds the requested data, satisfying the search query. For a more effective caching system, the hit ratio should be higher than the miss rate. One of the best ways to achieve that is to reduce cache misses.

Do cache misses increase latency?

Cache misses will add latency that otherwise would not have been incurred in a system without a cache. However, in a properly configured cache, the speed benefits that are gained from cache hits more than make up for the lost time on cache misses.