Miss Penalty refers to the extra time required to bring the data into cache from the Main memory whenever there is a “miss” in the cache.Miss penalty is the amount of time required to retrieve the data once you miss in the cache. Because we are dealing with a single-level cache, the only other level in the memory hierarchy to consider is main memory for the miss penalty.

What is meant by cache miss penalty?

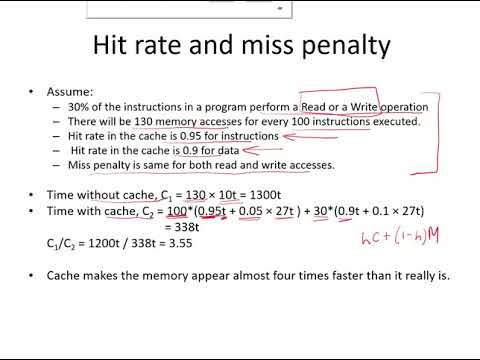

Miss penalty is defined as the difference between lower level access time and cache access time. Then the above equation becomes effective-access-time = cache-access-time + miss-rate * miss-penalty.

How is miss penalty calculated in cache?

You can calculate the miss penalty in the following way using a weighted average: (0.5 * 0ns) + (0.5 * 500ns) = (0.5 * 500ns) = 250ns . Now, suppose you have a multi-level cache i.e. L1 and L2 cache. Hit time now represents the amount of time to retrieve data in the L1 cache.

What is a miss in caching?

A cache miss is an event in which a system or application makes a request to retrieve data from a cache, but that specific data is not currently in cache memory. Contrast this to a cache hit, in which the requested data is successfully retrieved from the cache.

What is miss rate in cache memory?

Similarly, the miss rate is the number of total cache misses divided by the total number of memory requests made to the cache. One might also calculate the number of hits or misses on reads or writes only. Clearly, a higher hit rate will generally result in higher performance.

What is meant by cache miss penalty?

Miss penalty is defined as the difference between lower level access time and cache access time. Then the above equation becomes effective-access-time = cache-access-time + miss-rate * miss-penalty.

How is miss penalty calculated in cache?

You can calculate the miss penalty in the following way using a weighted average: (0.5 * 0ns) + (0.5 * 500ns) = (0.5 * 500ns) = 250ns . Now, suppose you have a multi-level cache i.e. L1 and L2 cache. Hit time now represents the amount of time to retrieve data in the L1 cache.

What is the miss penalty to main memory in cycles?

The miss penalty is the time to copy data from main memory to the cache. This often requires dozens of clock cycles (at least). The miss rate is the percentage of misses. The average memory access time, or AMAT, can then be computed.

What are the L1 L2 and L3 caches?

The main difference between L1 L2 and L3 cache is that L1 cache is the fastest cache memory and L3 cache is the slowest cache memory while L2 cache is slower than L1 cache but faster than L3 cache. Cache is a fast memory in the computer. It holds frequently used data by the CPU.

What is a good cache hit ratio?

A cache hit ratio of 90% and higher means that most of the requests are satisfied by the cache. A value below 80% on static files indicates inefficient caching due to poor configuration.

How do you reduce misses capacity?

Cache misses can be reduced by changing capacity, block size, and/or associativity. The first step to reducing the miss rate is to understand the causes of the misses. The misses can be classified as compulsory, capacity, and conflict.

Is cache miss an exception?

No, it simply causes a processor stall. Perhaps an appropriate mental image is of one or more NOP instructions getting inserted into the pipeline.

How miss rate and miss penalty are minimized?

The smaller first-level cache to fit on the chip with the CPU and fast enough to service requests in one or two CPU clock cycles. Hits for many memory accesses that would go to main memory, lessening the effective miss penalty.

How slow is a cache miss?

A cache miss occurs when a cache doesn’t have the requested data in its memory. Meanwhile, a hit is when a cache successfully finds the requested data, satisfying the search query. For a more effective caching system, the hit ratio should be higher than the miss rate.

How can the cache miss rate be reduced?

Cache misses can be reduced by changing capacity, block size, and/or associativity. The first step to reducing the miss rate is to understand the causes of the misses. The misses can be classified as compulsory, capacity, and conflict.

How many cycles does a cache miss take?

An L2 miss is at least 600 cycles. Cache is everything in performance; CPUs are so much faster than memory now that you’re really almost optimizing for the memory bus instead of the core.

Which technique used to reduce the miss penalty for improving cache performance?

Let’s take a look at some other techniques for reducing the miss penalty. This technique is used with write-through or write-back. The idea is not to make the CPU wait for the write to complete in memory. Instead, data is written to a write buffer, and the processor can continuef while it is being written to memory.

How can we avoid compulsory misses?

One way of reducing the number of capacity and compulsory misses is to use prefetch tech- niques such as longer cache line sizes or prefetching methods [9, 1]. However, line sizes can not be made arbitrarily large without increasing the miss rate and greatly increasing the amount of data to be transferred.06.08.1990

What is meant by cache miss penalty?

Miss penalty is defined as the difference between lower level access time and cache access time. Then the above equation becomes effective-access-time = cache-access-time + miss-rate * miss-penalty.

How is miss penalty calculated in cache?

You can calculate the miss penalty in the following way using a weighted average: (0.5 * 0ns) + (0.5 * 500ns) = (0.5 * 500ns) = 250ns . Now, suppose you have a multi-level cache i.e. L1 and L2 cache. Hit time now represents the amount of time to retrieve data in the L1 cache.

What is a miss in caching?

A cache miss is an event in which a system or application makes a request to retrieve data from a cache, but that specific data is not currently in cache memory. Contrast this to a cache hit, in which the requested data is successfully retrieved from the cache.

What is the miss penalty which is the amount of time to fill a cache block in terms of CPU clock cycles?

What is a cache miss?

A cache miss requires the system or application to make a second attempt to locate the data, this time against the slower main database. If the data is found in the main database, the data is then typically copied into the cache in anticipation of another near-future request for that same data.

What are the components of a miss penalty?

This include the time to access the block, transmit it from one level to the other, insert it in the level that experienced the miss and then pass the block to the requester. The time to access the next level in the hierarchy is the major component of the miss penalty.

How do you calculate the miss rate of a single-level cache?

Because we are dealing with a single-level cache, the only other level in the memory hierarchy to consider is main memory for the miss penalty. Here’s a good example for single-level cache: L1 cache has an access time of 5ns and a miss rate of 50% Main memory has an access time of 500ns AMAT = 5ns + 0.5 * 500ns = 255ns

Do cache misses increase latency?

Cache misses will add latency that otherwise would not have been incurred in a system without a cache. However, in a properly configured cache, the speed benefits that are gained from cache hits more than make up for the lost time on cache misses.